SiTime驅(qū)動負(fù)載單端振蕩器的終端建議

來源:http://m.wyss.net.cn 作者:金洛鑫電子 2019年08月13

SiTime Corp.公司是專注于MEMS振蕩器設(shè)計,開發(fā),研究,制造和銷售的生產(chǎn)廠家.幾十年來不斷鉆研和創(chuàng)新新的技術(shù),從2005年開始發(fā)現(xiàn)了降低MEMS晶振成本的方法,使MEMS得到大力的發(fā)展.因此,MEMS也在這十幾年里突飛猛進(jìn),同時也提升了SiTime晶振的品牌效應(yīng)和口碑,成為我國重要的進(jìn)口晶振供應(yīng)商之一.SiTime有一項(xiàng)技術(shù)可以驅(qū)動單個或多個負(fù)載單端晶體振蕩器終端的方法,詳情請閱讀本文!

具有快速邊沿的時鐘信號將印刷電路板(PCB)上的跡線視為傳輸線而不是簡單的導(dǎo)線連接.如果PCB走線的長度超過一定限度,則需要將走線阻抗與源和負(fù)載阻抗中的一個或兩個匹配.阻抗不匹配導(dǎo)致信號反射在傳輸線中來回傳播,從而導(dǎo)致信號失真,例如振蕩,過沖和下沖.本Oscillator應(yīng)用筆記提供了正確終止主要由LVCMOS輸出驅(qū)動的單端走線的指南.本文檔討論了單負(fù)載和多負(fù)載方案.

Lumped與分布式PCB走線

如果響應(yīng)輸入信號,所有點(diǎn)與均勻電位一起反應(yīng),則時鐘源,PCB走線和時鐘接收器被認(rèn)為是集總系統(tǒng).如果響應(yīng)沿跟蹤分布,則系統(tǒng)稱為分布式系統(tǒng).任何環(huán)境中信號傳播的速度都是有限的,因此不存在完美的集總系統(tǒng).通常的做法是將PCB走線的長度與最快時鐘信號邊沿的有效長度進(jìn)行比較,并使用該比率來判斷系統(tǒng)是否可以視為集總系統(tǒng).跟蹤中的有效信號邊長計算如下:

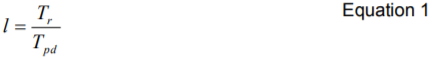

其中l(wèi)=上升沿的長度,in.

Tr=10%-90%的上升時間,ps

Tpd=每單位長度的傳播延遲,ps/in.

例如,FR4PCB走線中的傳播延遲范圍為140至180ps/in.假設(shè)Tpd=150ps/in.1ns上升沿的有效長度為6.7in.

如果PCB走線的長度小于或等于信號邊沿有效長度的六分之一(1/6),則該電路主要以點(diǎn)燈方式工作.當(dāng)比較20%-80%的上升/下降時間時,更合適的比例是l/4來決定是否可以將跡線視為集總元素.集總電路不需要終止.例如,假設(shè)時鐘信號具有1ns10%-90%的上升時間且FR4PCB材料走線長于1.1in,則必須將其視為傳輸線.

有關(guān)不同負(fù)載選項(xiàng)和驅(qū)動強(qiáng)度設(shè)置的SiTime晶振的上升和下降時間表可在大多數(shù)器件系列的數(shù)據(jù)表中找到.使用公式1時,從數(shù)據(jù)表上升/下降時間表(通常為5pF)中選擇最低負(fù)載選項(xiàng),因?yàn)榻邮掌鱾?cè)的容性負(fù)載不會影響驅(qū)動傳輸線時源的上升/下降時間.

當(dāng)時鐘驅(qū)動器將邊沿發(fā)送到傳輸線時,邊沿經(jīng)過一段延遲后到達(dá)負(fù)載.如果負(fù)載的阻抗(Z1)不同于傳輸線的阻抗(Z0),則信號的一部分從負(fù)載朝向源反射.源處的不匹配導(dǎo)致部分反射信號反射回負(fù)載(圓尖反射).反射信號的分?jǐn)?shù)由反射系數(shù)[附錄B]確定.以下部分描述了終端策略,可用于在驅(qū)動單個或多個負(fù)載時最小化反射并改善信號完整性.

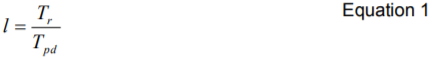

用于驅(qū)動單負(fù)載的源終端 串聯(lián)端接是通過在走線附近插入一個盡可能靠近源的電阻來構(gòu)建的(見圖1).為了獲得適當(dāng)?shù)淖杩蛊ヅ?時鐘驅(qū)動器和串聯(lián)終端電阻的輸出阻抗應(yīng)等于走線阻抗,即:

Rs+Rd=Zo

其中Rs-終端電阻的值

Rd-驅(qū)動器的輸出阻抗

Z0-傳輸線阻抗

例如,我們計算適用于SiT8208器件的終端電阻值,該器件具有默認(rèn)驅(qū)動強(qiáng)度,工作電壓為3.3V,驅(qū)動60Ω走線.從晶振數(shù)據(jù)表2表4中我們確定默認(rèn)的驅(qū)動強(qiáng)度代碼是”F”.使用附錄C中的表1,我們確定具有驅(qū)動強(qiáng)度代碼”F”和3.3V工作電壓的SiT8208器件的典型輸出阻抗為15.3Ω.將走線阻抗和輸出阻抗代入公式2,我們計算源端接電阻值Rs=60Ω-15.3Ω=44.7Ω.

使用圖1中的配置,來自信號源的信號將沿著跡線傳播,直到達(dá)到負(fù)載.典型負(fù)載具有非常高的輸入阻抗(在兆歐范圍內(nèi)),因此不會吸收能量并且整個信號被反射回源.因?yàn)樵刺幍淖杩古c傳輸線的阻抗匹配,所以不會發(fā)生進(jìn)一步的反射.有關(guān)串聯(lián)端接傳輸線中信號傳播的詳細(xì)圖表.

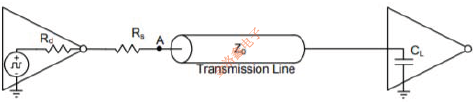

SiTime建議使用SiTime提供的貼片振蕩器IBIS模型來模擬布局.作為示例,我們使用AltiumDesigner軟件中的信號完整性分析工具來模擬驅(qū)動5英寸60Ω傳輸線的SiT8208振蕩器.圖2顯示了負(fù)載側(cè)模擬的信號波形.選擇終端電阻Rs=43Ω以匹配60Ω線路阻抗.終端電阻的相同值用于模擬+/-10%的跡線阻抗變化,因此考慮到PCB制造的擴(kuò)散. 圖2:SiT8208的Altium Designer仿真波形驅(qū)動負(fù)載通過傳輸線中的5.走線阻抗-54,60和66Ω,電源電壓-3.3V,源端接-43Ω,負(fù)載電容-5pF.有關(guān)SiTime單端振蕩器典型輸出阻抗的信息.

具有快速邊沿的時鐘信號將印刷電路板(PCB)上的跡線視為傳輸線而不是簡單的導(dǎo)線連接.如果PCB走線的長度超過一定限度,則需要將走線阻抗與源和負(fù)載阻抗中的一個或兩個匹配.阻抗不匹配導(dǎo)致信號反射在傳輸線中來回傳播,從而導(dǎo)致信號失真,例如振蕩,過沖和下沖.本Oscillator應(yīng)用筆記提供了正確終止主要由LVCMOS輸出驅(qū)動的單端走線的指南.本文檔討論了單負(fù)載和多負(fù)載方案.

Lumped與分布式PCB走線

如果響應(yīng)輸入信號,所有點(diǎn)與均勻電位一起反應(yīng),則時鐘源,PCB走線和時鐘接收器被認(rèn)為是集總系統(tǒng).如果響應(yīng)沿跟蹤分布,則系統(tǒng)稱為分布式系統(tǒng).任何環(huán)境中信號傳播的速度都是有限的,因此不存在完美的集總系統(tǒng).通常的做法是將PCB走線的長度與最快時鐘信號邊沿的有效長度進(jìn)行比較,并使用該比率來判斷系統(tǒng)是否可以視為集總系統(tǒng).跟蹤中的有效信號邊長計算如下:

其中l(wèi)=上升沿的長度,in.

Tr=10%-90%的上升時間,ps

Tpd=每單位長度的傳播延遲,ps/in.

例如,FR4PCB走線中的傳播延遲范圍為140至180ps/in.假設(shè)Tpd=150ps/in.1ns上升沿的有效長度為6.7in.

如果PCB走線的長度小于或等于信號邊沿有效長度的六分之一(1/6),則該電路主要以點(diǎn)燈方式工作.當(dāng)比較20%-80%的上升/下降時間時,更合適的比例是l/4來決定是否可以將跡線視為集總元素.集總電路不需要終止.例如,假設(shè)時鐘信號具有1ns10%-90%的上升時間且FR4PCB材料走線長于1.1in,則必須將其視為傳輸線.

有關(guān)不同負(fù)載選項(xiàng)和驅(qū)動強(qiáng)度設(shè)置的SiTime晶振的上升和下降時間表可在大多數(shù)器件系列的數(shù)據(jù)表中找到.使用公式1時,從數(shù)據(jù)表上升/下降時間表(通常為5pF)中選擇最低負(fù)載選項(xiàng),因?yàn)榻邮掌鱾?cè)的容性負(fù)載不會影響驅(qū)動傳輸線時源的上升/下降時間.

當(dāng)時鐘驅(qū)動器將邊沿發(fā)送到傳輸線時,邊沿經(jīng)過一段延遲后到達(dá)負(fù)載.如果負(fù)載的阻抗(Z1)不同于傳輸線的阻抗(Z0),則信號的一部分從負(fù)載朝向源反射.源處的不匹配導(dǎo)致部分反射信號反射回負(fù)載(圓尖反射).反射信號的分?jǐn)?shù)由反射系數(shù)[附錄B]確定.以下部分描述了終端策略,可用于在驅(qū)動單個或多個負(fù)載時最小化反射并改善信號完整性.

用于驅(qū)動單負(fù)載的源終端 串聯(lián)端接是通過在走線附近插入一個盡可能靠近源的電阻來構(gòu)建的(見圖1).為了獲得適當(dāng)?shù)淖杩蛊ヅ?時鐘驅(qū)動器和串聯(lián)終端電阻的輸出阻抗應(yīng)等于走線阻抗,即:

Rs+Rd=Zo

其中Rs-終端電阻的值

Rd-驅(qū)動器的輸出阻抗

Z0-傳輸線阻抗

例如,我們計算適用于SiT8208器件的終端電阻值,該器件具有默認(rèn)驅(qū)動強(qiáng)度,工作電壓為3.3V,驅(qū)動60Ω走線.從晶振數(shù)據(jù)表2表4中我們確定默認(rèn)的驅(qū)動強(qiáng)度代碼是”F”.使用附錄C中的表1,我們確定具有驅(qū)動強(qiáng)度代碼”F”和3.3V工作電壓的SiT8208器件的典型輸出阻抗為15.3Ω.將走線阻抗和輸出阻抗代入公式2,我們計算源端接電阻值Rs=60Ω-15.3Ω=44.7Ω.

使用圖1中的配置,來自信號源的信號將沿著跡線傳播,直到達(dá)到負(fù)載.典型負(fù)載具有非常高的輸入阻抗(在兆歐范圍內(nèi)),因此不會吸收能量并且整個信號被反射回源.因?yàn)樵刺幍淖杩古c傳輸線的阻抗匹配,所以不會發(fā)生進(jìn)一步的反射.有關(guān)串聯(lián)端接傳輸線中信號傳播的詳細(xì)圖表.

SiTime建議使用SiTime提供的貼片振蕩器IBIS模型來模擬布局.作為示例,我們使用AltiumDesigner軟件中的信號完整性分析工具來模擬驅(qū)動5英寸60Ω傳輸線的SiT8208振蕩器.圖2顯示了負(fù)載側(cè)模擬的信號波形.選擇終端電阻Rs=43Ω以匹配60Ω線路阻抗.終端電阻的相同值用于模擬+/-10%的跡線阻抗變化,因此考慮到PCB制造的擴(kuò)散. 圖2:SiT8208的Altium Designer仿真波形驅(qū)動負(fù)載通過傳輸線中的5.走線阻抗-54,60和66Ω,電源電壓-3.3V,源端接-43Ω,負(fù)載電容-5pF.有關(guān)SiTime單端振蕩器典型輸出阻抗的信息.

正在載入評論數(shù)據(jù)...

相關(guān)資訊

- [2024-03-08]IQD晶體尺寸縮小的設(shè)計效果LFXT...

- [2024-03-07]Golledge衛(wèi)星通信中的頻率控制產(chǎn)...

- [2024-03-07]Golledge工業(yè)自動化和控制系統(tǒng)中...

- [2024-03-06]MTI-milliren恒溫晶振222系列振...

- [2024-03-06]MTI-milliren低G靈敏度銫原子鐘...

- [2024-03-05]GEYER高穩(wěn)定性KXO-V93T低功耗32...

- [2024-03-02]NEL為系統(tǒng)關(guān)鍵應(yīng)用程序設(shè)計和制...

- [2024-01-06]溫補(bǔ)補(bǔ)償振蕩器的原理及特點(diǎn)

業(yè)務(wù)經(jīng)理

業(yè)務(wù)經(jīng)理 客服經(jīng)理

客服經(jīng)理